International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

An ISO 3297: 2007 Certified Organization

Vol. 5, Special Issue 4, March 2016

National Conference on Signal Processing, Instrumentation and Communication Engineering (SPICE' 16)

Organized by

Dept. of ECE, Mar Baselios Institute of Technology & Science (MBITS), Kothamangalam, Kerala-686693, India

# Full Coverage Area with Better Image Capturing Using Sensible MCEC for Medical Scrutiny Applications

Arathi Narendranathan

PG Student (CE), Dept. of ECE, Royal College of Engineering & Technology Thrissur, India

**ABSTRACT:** This paper propose a replacement methodology for endoscopic capsules to scale back the miss rate of wireless endoscopy. In this application, we are using a Micro-Ball epitome with Six sensible cameras inside an endoscopic capsules focusing to increase the visual area inside the human alimentary canal. Endoscopic Capsules consists of a master-slave design of associate economical Bus Architecture and a Four-level Clock Management in it. The cameras are employed with movement sensitive control and smart, sensitive image capturing enables a full coverage area of alimentary canal with low power consumption. By this, we can increase the operating life of an endoscopic capsule with low complexity image compressor and it will enhance the coverage rate of MCEC to 98% and power consumption within 7.1 mW.

**KEYWORDS:** Multiple camera endoscopy, image capturing & compression, movement sensitive control, camera selection and data storage.

#### I. INTRODUCTION

Wireless Capsule Endoscopy (WCE) a breakthrough has proven to be the endoscopic investigation of choice for visualization of the entire bowel. Primarily capsule endoscopy is used to examine areas of small intestine that can't be seen by other endoscopic methods. Due to limited visual field and low image acquisition rate, random movement of WCE leads to high miss rate mainly in stomach and colon of alimentary (GI) tract. To overcome all these considering size and power restrictions various methods has been developed by researchers and companies. One was by increasing cameras for large visual area. Higher power consumption due to high image acquisition rate is not supported well by the coin batteries inside the capsules leading to a small battery life. To overcome all power, size restrictions, patient friendly considering human safety's proposing a new method of design of Multiple Cameras Endoscopic Capsules (MCEC) to reduce the miss rate and for getting larger visual area. MCEC stores image data into the flash memory for getting high image acquisition rate instead of wireless transmission. With movement and attitude information basis of image control strategy reduces negative impact of random movement of capsule in GI tract.

Master-slave architecture is implemented to face the challenges of low power consumption and miniaturization in MCEC. Efficient bus architecture and four level clock management architecture is applied for reducing power consumption. The image data stored in MCEC need to be retained for diagnosis after its evacuation. To avoid disassembly and connecting wires during complicated surgeries for doctors, data reader considering above features are used. Limitation of data bandwidth to increase image acquisition rate by flash memory may also leads to an increase in power consumption. So we go for image compression techniques, an image compressor with modified JPEG image compression algorithms is used to avoid computational complexity and memory space.

#### II. MULTIPLE CAMERAS ENDOSCOPIC CAPSULE ARCHITECTURE DESIGN

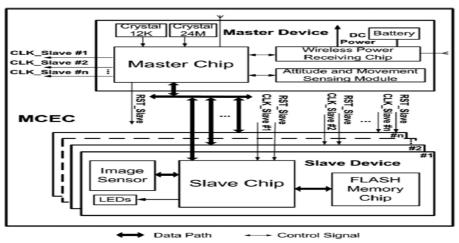

### A. Master-slave Architecture

To enlarge vision field by using multiple cameras may causes complexity in integrating all the modules in a MCEC without increasing power. So it uses master-slave architecture for the system integration. Master device being a core part consists of master controller, power supply and clock management and slave device for image acquisition tasks like image-capturing, compression and storage with a simplified, organized and flexible system. Master chip performs

#### International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

An ISO 3297: 2007 Certified Organization

Vol. 5, Special Issue 4, March 2016

# National Conference on Signal Processing, Instrumentation and Communication Engineering (SPICE' 16) Organized by

Dept. of ECE, Mar Baselios Institute of Technology & Science (MBITS), Kothamangalam, Kerala-686693, India the whole wireless communication where the slave chip performs image compression function. The chip receiving wireless power provides stable DC power.

Fig. 1: MCEC's System Level Diagram

A tradeoff has been chosen between the hardware cost and the performance for commercial modules in MCEC. For miniaturization a ruling body with a control mode is used in which the master- slave communicates and they perform their own functions of their corresponding modules. In flash memory module, all the image sensors are incorporated into it by distributed storage mode and thereby reducing individual flash memory chip size on the slave device and is energy efficient in data transfer.

Fig. 2: a) Central Control Mode, b) Hierarchy Control Mode, c) Central Storage, d) Hybrid Storage Mode

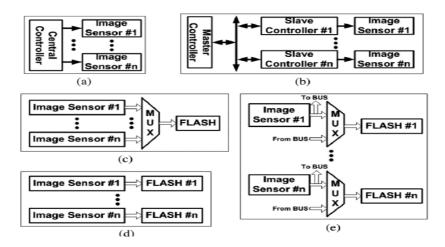

### B. Bus Architecture And Four-Level Clock Management

Bus Architecture provides efficient data transfer between the devices reduces the power consumption. The two phases, one is Master Command Phase (MCP) with low power consumption and the other Slave Data Phase (SDP) with high data rate. Power consumption of bus transmission is

$$P = \mathbf{1} + 2(V^2 \times f) \sum_{i=1}^{n} piCi$$

(1)

#### International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

An ISO 3297: 2007 Certified Organization

Vol. 5, Special Issue 4, March 2016

# National Conference on Signal Processing, Instrumentation and Communication Engineering (SPICE' 16) Organized by

Dept. of ECE, Mar Baselios Institute of Technology & Science (MBITS), Kothamangalam, Kerala-686693, India where, V is the bus voltage, f is the synchronization clock frequency, pi is the transition probability of one data wire and Ci is the capacitance load of the data wire.

The data wires are bidirectional for reducing the number of wire connections. First and second level clock management is set in the master device and third in the slave device and in the fourth level each module has its own clock management shows power saving of 28% in the MCEC.

Fig. 3: Four Level Clock Management

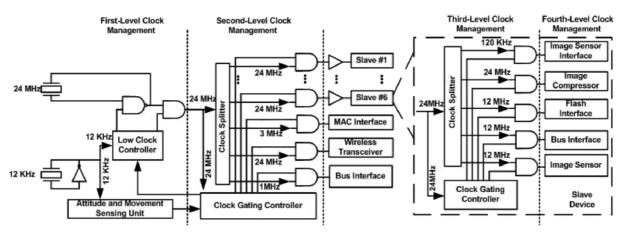

#### C. MCE System Architecture

This part consists of a swallow-able MCEC, data reader for image restoration after evacuation and a workstation for display and post-processing the image in it. Wireless Power Transmission (WPT) module of data reader establishes a wireless power link between MCEC and data reader and in turn a wireless data link can be achieved via transceivers in MCEC and data reader and from there it is read out via PC to the workstation.

Fig. 5: Wireless Power Receiving Chip Architecture

#### International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

An ISO 3297: 2007 Certified Organization

Vol. 5, Special Issue 4, March 2016

National Conference on Signal Processing, Instrumentation and Communication Engineering (SPICE' 16)

Organized by

Dept. of ECE, Mar Baselios Institute of Technology & Science (MBITS), Kothamangalam, Kerala-686693, India

The wireless power receiving chip contains 3 Rx circuits, which are actually the projected high potency CMOS rectifiers with current Zero-Cross-Point (ZCP) prediction [17]. They work independently and support 3 receiving coils for position receiving. so as to create full use of received energy, the chip conjointly contains an influence combination circuit, which is actually the projected Skipping Booster [17]. It combines the received energy from all directions along and delivers to the low dropout regulator (LDO). This chip can also deliver the energy from coin batteries to the LDO and also the alternative between wireless power and batteries is determined by the management signal.

### III. SMART IMAGE CAPTURE STRATEGY

To avoid miss rate due to random movement and size of MCEC in the GI tract a smart image capturing strategy based on its movement sensitive control of image frame rate and attitude information for camera selection is implemented. Accelerometers used for motion detection using an algorithm,

$$if \ th1 < F\left(\|\underset{at}{\rightarrow} - \underset{t-1}{\overrightarrow{a}}\|\right) \le th2, \text{ motion state detected}$$

elseif

$$h2 < F\left(\|\underset{at}{\rightarrow} - \underset{at}{\overrightarrow{a}}\|\right), \text{ drastic motion state detected}$$

(2)

else, no motion detected.

where, is the acceleration at th sample value, F denotes moving average filter for reducing noise. th1 and th2 are two thresholds.

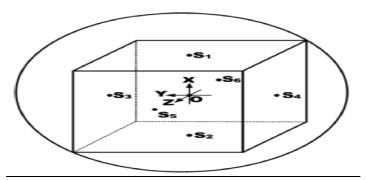

And camera selection with attitude information using six camera endoscopy called 'Micro-Ball,' is used. Set with different cameras selected at different time will have different orientations. The perspective data of the MCEC represents its rotation standing. The camera choice strategy will make sure that the cameras hand-picked throughout a picture capture amount have completely different orientations to the alimentary tract wall. Hence, the captured pictures will cover the maximum amount space of the alimentary tract wall as attainable. Camera choice is a scheme based on the image capture period.

Fig.6: Camera Selection Co-ordinates

The computation of the DCM is that the key step within the camera selection rule. Considering that the quantity of cameras to be designated and every camera's field of read, the DCM computation accuracy demand isn't terribly high. Therefore we have a tendency to solely select the gauss meter and also the measuring system for the DCM computation. Compared with the common navigation system, the projected design doesn't use a gyro thanks to its high power consumption [25], [26]. The DCM (Direct Cosine Matrix) is decided by the gravity and geomagnetic field vectors measured at totally different times.

Copyright to IJAREEIE <a href="www.ijareeie.com">www.ijareeie.com</a> 199

#### International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

An ISO 3297: 2007 Certified Organization

Vol. 5, Special Issue 4, March 2016

## National Conference on Signal Processing, Instrumentation and Communication Engineering (SPICE' 16) Organized by

Dept. of ECE, Mar Baselios Institute of Technology & Science (MBITS), Kothamangalam, Kerala-686693, India Camera selection at time  $T_n$  can be obtained by,

$$m = \operatorname{argmin} \parallel D_{m,n} - D_{n,1} \parallel_{L} \tag{3}$$

For n=2, 3,...,6:  $D_{m,n}=M_m D_{n,1}$ , where  $M_n$  denotes DCM.

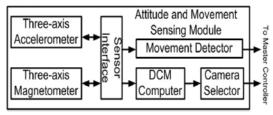

In order to comprehend the image frame rate management and camera selection, associate degree angle and Movement Sensing Module (AMSM) is projected. Considering that this module is embedded within the MCEC, little size and low power consumption square measure the chief design necessities. Therefore, we decide extremely integrated MEMS sensors for the gauss meter and also the measuring device. The results of the movement detector are employed for the image frame rate management and also the results of the DCM pc is sent to the camera selector for camera choice. AMSM's power consumption can be less than 1mW.

Fig. 7: AMSM Architecture

### IV. IMAGE COMPRESSION AND STORAGE

The application of the image storage strategy will save the power consumption. However, from the facility simulation analysis, it is found that the facility consumed by the image storage still accounts for about four-hundredth of the entire power consumption without compression. Hence, the appliance of compression before image storage will considerably reduce the entire power consumption of the MCEC. Moreover, the compression will scale back the non-volatile storage capability needed. Hence, it's terribly useful for the miniaturization of the MCEC.

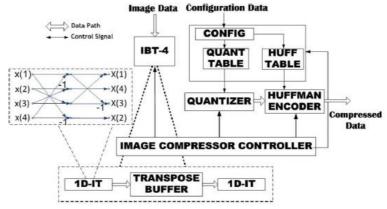

Considering the trade-off between the compression performance and the computation complexness, a changed JPEG image compression algorithmic rule has been projected. For low machine complexity and little buffer house, a replacement 4 × 4 whole number Block remodel (IBT-4) is projected for the compression. The quantization table is optimized on the idea of the rate-distortion theory [29], and also the parts of the division table square measure set to for eliminating the division operations. The compression algorithm is developed for aspirin Color Filter Array (CFA) pattern of the CMOS image sensing element. R, G and B color elements use an equivalent division table to additional cut back the hardware complexity. The Huffman secret writing algorithmic rule is chosen for the entropy secret writing once the division stage is done.

Fig. 8 Image Compressor Architecture

International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

An ISO 3297: 2007 Certified Organization

Vol. 5, Special Issue 4, March 2016

National Conference on Signal Processing, Instrumentation and Communication Engineering (SPICE' 16)

Organized by

Dept. of ECE, Mar Baselios Institute of Technology & Science (MBITS), Kothamangalam, Kerala-686693, India

Fig. 9: Original Vs Reconstructed WCE Images

The image compressed is then stored inside the flash memory module.

|                               | Master Chip           | Slave Chip             |

|-------------------------------|-----------------------|------------------------|

| Techonology                   | 0.18 μ m 1P6M<br>CMOS | 0.18 µ m 1P6M<br>CMOS  |

| Chip area                     | 3.8mm×3.7mm           | 3.8mm×3.7mm            |

| Chip area(digital core)       | 2.0mm×1.0mm           | 2.1mm×2.0mm            |

| On-Chip memory                | 2KB dual port SRAM    | 10KB dual port<br>SRAM |

| Supply voltage(digital core)  | 1.8V to 1.2V          | 1.8V to 1.2V           |

| Clock frequency               | 24MHz/12KHz           | 24MHz                  |

| Input Image resolution        | /                     | 480×480/240×240        |

| Input Image frame rate        | /                     | 1fps~24fps             |

| Wireless Transmitting<br>Rate | 3Mbps                 | /                      |

| Wireless Receiving<br>Rate    | 64Kbps                | /                      |

Fig. 10: Chipset Performance Table

After testing it has been noticed with a 33% of power consumption can be preserved with this image compressing method.

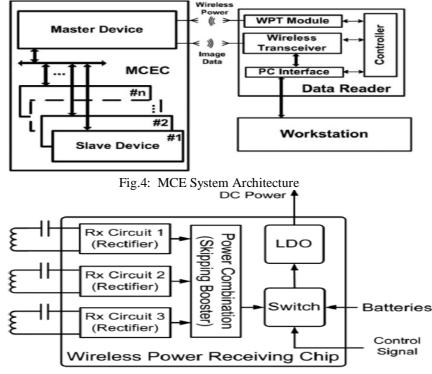

## V. MCEC IMPLEMENTATION

The master chip, slave chip and wireless power receiving chip square measures fictitious in 0.18  $\mu$ m 1P6M technology. The wireless transceiver contains additional high metal than the digital core, so it's additional decipherable within the die icon. After the MCEC is exhausted, it is powered by wireless power transmission and starts image information transmission only at that time. So, the ability consumption restriction throughout the data transmission amount isn't thus strict as that in the amount of getting pictures. The wireless power receiving chip with a 1.5mm  $\times$  1.5mm die area can deliver a stable DC power for the MCEC.

International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

An ISO 3297: 2007 Certified Organization

Vol. 5, Special Issue 4, March 2016

National Conference on Signal Processing, Instrumentation and Communication Engineering (SPICE' 16)

Organized by

Dept. of ECE, Mar Baselios Institute of Technology & Science (MBITS), Kothamangalam, Kerala-686693, India

#### A. Micro-Ball

A PCB cube with six cameras is often sealed into a clear biocompatible plastic shell to create a 'Micro-Ball'. If tiny size non volatile storage chip are often got, a more compact Micro-Ball are often enforced and be used for the GI tract examination.

Fig.11: Micro-Ball

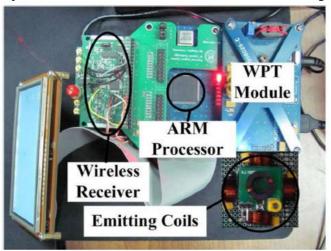

#### B. Data Reader

The Data Reader employs ARM processor as the controller. The WPT module and emitting coils are unit customized.

Fig. 12 Data Reader

The Micro-Ball prototype's power consumption diagram of getting a frame of  $480 \times 480$  image with the proposed compression and while not compression. The remarkable distinction between the 2 things is marked by the red circle. It is seen that the amount of program operations is considerably ablated once compression. The total energy consumption is reduced around 33%. The energy consumed for getting a frame of  $480 \times 480$  image with the projected compression is barely around 2.6 mJ.

| Image<br>Frame rate<br>(480×480) | Power consumption of<br>Master Chip (1.8V<br>supply/1.2V Supply) | Power consumption of<br>Slave Chip (1.8V<br>supply/1.2V Supply) |

|----------------------------------|------------------------------------------------------------------|-----------------------------------------------------------------|

| 1                                | 0.6 mW/0.25 mW                                                   | 1.6 mW/0.7 mW                                                   |

| 2                                | 1.1 mW/0.5 mW                                                    | 3 mW/1.5mW                                                      |

| 6                                | 2.6 mW/1.4 mW                                                    | 8.1 mW/4 mW                                                     |

| 24                               | 10mW/5 mW                                                        | 29mW/16 mW                                                      |

Fig. 13: Power Consumption of Chipset

#### International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

An ISO 3297: 2007 Certified Organization

Vol. 5, Special Issue 4, March 2016

National Conference on Signal Processing, Instrumentation and Communication Engineering (SPICE' 16)

Organized by

Dept. of ECE, Mar Baselios Institute of Technology & Science (MBITS), Kothamangalam, Kerala-686693, India

#### VI. CONCLUSION

In this paper, we tend to project a sensible MCEC for medical scrutiny applications. With multiple cameras and better image capturing facility, the MCEC will cowl a relatively giant space of the alimentary canal wall. The power consumption will be considerably reduced with the projected efficient master-slave design and low complexity image compressor. The energy consumed for capture an impression of  $480 \times 480$  image is only around 2.6 mJ. The coverage rate of the capsule paradigm can achieve 98% through the smart image capture mode and the power consumption is barely around 7.1 mW. The said mentioned designs alter the MCEC to expeditiously do the diagnosing of the complete human alimentary canal.

### REFERENCES

- [1] G. Iddan, G. Meron, and A. Glukhovsky et al., "Wireless Capsule Endoscopy," Nature, vol. 405, pp. 417–418, May 25, 2000

- [2] T. Nakamura and A. Terano, "Capsule endoscopy: Past, present, future," J. Gastroenterol., vol. 43, no. 2, pp. 93–99, 2008.

- [3]S. Bar-Meir and M. B. Wallace, "Diagnostic colonoscopy: The end is coming," Gastroenterol, vol. 131, pp. 992–994, 2006.

- [4] N. Schoofs, J. Deviere, and A. Van Gossum, "Pillcam colon capsule endoscopy compared with colonoscopy for colorectal tumor diagnosis: A prospective pilot study," Endoscopy, vol. 38, pp. 971–977, 2006.

- [5] P. Demosthenous and J. Georgiou, "Acceleration-dependent sampling for ingestible endoscopic imaging capsule," in *Proc. IEEE* Biomedical Circuits and Systems *Conf.*, Nov. 28–30, 2012, pp. 1–4.

- [6] S. Tognarelli, C. Quaglia, P. Valdastri, E. Susilo, A. Menciassi, and P.Dario, "Innovative stopping mechanism for esophageal wireless capsular endoscopy," in Proc. 23rd Eurosensors Conf., 2009, pp. 485–488.